面向片外不可信内存的一种实用ORAM方案

濮传威 张功萱 周俊龙 付安民

(南京理工大学计算机科学与工程学院 南京 210094)

为了防止信息通过内存总线泄露,研究者们已经提出了安全处理器模型,例如XOM[1],AEGIS[2],SGX[3].安全处理器模型主要依靠数据加密确保系统安全性.

然而,单独使用数据加密已经不足以保护系统的安全性,因为每次内存访问仍然需要明文内存地址.攻击者仍然可以通过总线窥探访问的内存地址从而获得隐式信息[4],如图1所示.因此,内存地址被访问的顺序(即内存访问模式,简称访问模式)可以暴露正在运行的程序和数据的大量敏感信息.例如,观察指令的执行顺序可以揭示程序执行的转移方式、循环次数以及访问某个内存地址的频率等.

图1 窥探安全处理器的总线获得隐式信息

鉴于此,有研究者们提出了不经意随机访问机(oblivious random access machine, ORAM)[5-6].ORAM是一种加密原语,它将每次对存储器的真实访问转换为一系列随机访问,从而隐藏真实访问.ORAM最初作为一种软件算法由Goldreich[5]提出,用于隐藏客户端对远程云存储的访问模式,该算法具有非常大的性能开销.在ORAM的最初提议之后,研究者们一直在努力寻找一种在加密方面更安全、更可行的ORAM方案.

ORAM的概念也被考虑在处理器—内存级别,以隐藏处理器对片外不可信内存的访问模式[7-10].处理器对内存进行访问时,集成在片上的ORAM控制器会生成对片外内存的虚拟访问,这些虚拟访问从随机内存地址获取加密的数据块,对数据进行操作后重新加密并写回内存,使攻击者无法发现真实访问地址或访问类型.因此,ORAM在完成访问时会产生巨大的延迟,使得ORAM对于大多数应用程序都是不切实际的,尤其是在硬件级别实现到处理器中时.

针对具有片外不可信内存的处理器系统,本文提出了一种可广泛实际应用的处理器—内存级的ORAM方案——分组ORAM(group ORAM).该方案在保证安全性的同时降低性能开销.与现有技术相比,其性能开销不会随着内存容量增加而增加,并与应用程序大小无关,因此对于大型应用程序具有高度可扩展性,从而降低了成本,并使ORAM概念实用化.同时,分组ORAM引入了参数化设计,可以调整参数以满足对性能、安全性的不同需求.

ORAM的概念最初由Goldreich[5]提出,以防止在访问远程不可信云存储设备时通过访问模式泄露信息.在现阶段ORAM是隐藏用户访问模式的主要方法.当用户访问存储在服务器的数据时,他们会同时访问有效数据和虚拟数据,这将混淆用户访问的目标数据,从而隐藏用户的访问行为[11-12].然而,ORAM在提高安全性的同时,会显著增加存储空间的负担和交互数据量,例如:为了混淆目标数据块,需要添加部分虚拟数据块,并且需要对不同数据块进行多次访问.如何在保证用户访问行为安全性的前提下提高ORAM的访问效率是一个挑战性问题.

另一种减少性能开销的方案是Goldreich等人[6]提出的分层ORAM(hierarchical ORAM).该方案将数据块组织成层次结构.需要lbN层来存储N个数据块.第i层包含2i个桶,每个桶又包含lbN个数据槽用于存储数据.每个层级中的数据块使用随机选择的散列函数存储在相应的桶中.对于每次数据访问,首先扫描2个顶部的桶,在其他每个较低层级上,只扫描1个桶(若数据未找到,则扫描该层级上由散列函数指定的桶;

若数据已找到,则随机扫描该层级上的1个桶).最后将找到的数据写入第1层的桶内.该方案对于每次数据访问的平均开销为O(lb4N),最坏情况下为O(Nlb3N).

分层ORAM方案由于客户端存储量小且层次结构中每个较高级别的数据块数量呈指数增长,因此随着层次结构中每个新层级的添加,数据打乱重组的开销会显著增加.这限制了分层ORAM的可伸缩性和性能.

实施和管理多个ORAM及其本地缓存的开销是很大的.针对这个问题,Shi等人[15]对分层ORAM进行了改进,进一步提出了Path ORAM[16],它以二叉树的形式存储数据.每个叶子节点代表1条路径,每个数据映射到1个叶子节点即1条路径.数据可以存储在该路径上的任意节点之中.使用位置图映射数据块所在路径;

并用缓冲区暂时存放访问的数据块.对于每次数据访问,Path ORAM找到该数据块所在的路径,并读取该路径上所有数据块,然后将它们解密后缓存到缓冲区中,再将请求数据块返回给处理器以进行读取或更新.然后将请求的数据块随机映射到新的路径上.Path ORAM对于每次数据访问在最好和最坏情况下的开销是相同的,即O(lbN).

基于Path ORAM算法,研究者们提出了多种Path ORAM原型系统(PHANTOM[7],Tiny ORAM[8],Secure Dimm[9],D-ORAM[10],Freecursive[17],ASCEND[18]),旨在实际环境中评估该算法的实用性.表1给出了现有ORAM原型系统的归纳.

表1 现有ORAM原型的归纳

尽管现有设计使ORAM实现成为可能,但它们的性能开销仍然很大.在第2节将给出一种分组ORAM方案,它在最佳和最坏情况下都具有O(1)的性能开销,即性能开销与应用程序大小无关,这使得它在处理器级系统设计上具有高度可扩展性.并且针对不同平台对安全性以及性能的要求,可以进行灵活配置.

2.1 分组ORAM方案设计

图2给出了带有分组ORAM的处理器系统的抽象视图.分组ORAM与处理器位于同一芯片上并被视为可信,而内存位于片外并被视为不可信,攻击者可以观察到被访问的数据及其地址.

图2 使用分组ORAM的处理器系统的抽象视图

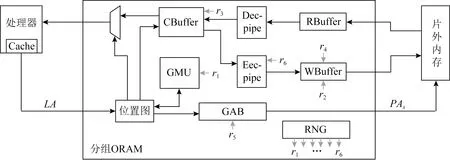

图3 分组ORAM体系结构

处理器在每次Cache未命中时通过分组ORAM访问片外内存.为了访问数据块,处理器指定其逻辑地址LA要执行的操作op(读/写)和要写入的数据data(如果操作是写入).分组ORAM将内存访问请求的逻辑地址转换为随机物理地址访问序列{PA1,PA2,…}.

分组ORAM所需的应用程序的逻辑存储空间由2部分组成:应用程序空间(application space)和虚拟空间(dummy space).假设应用程序大小为N个数据块,虚拟空间为D个数据块,则对于该应用程序,分组ORAM所需的总内存空间为N+D.虚拟空间仅对分组ORAM可见,而应用程序空间对处理器和分组ORAM均可见.类似地,包含应用程序数据的数据块称为真实块(true block),包含虚拟数据的数据块称为虚拟块(dummy block).

与其他现有方案类似,分组ORAM方案将执行1组任务以隐藏访问模式:选择1组数据块,解密该组数据块(将其中真实访问的数据块返回给处理器),将该组数据块与ORAM缓存中的块进行随机排列,再将其重新加密,并写入内存.这组基本任务统称为ORAM操作.ORAM操作将真实内存访问转换为一系列虚拟访问以覆盖真实访问从而隐藏访问模式.

2.2 分组ORAM结构

图3示出分组ORAM的体系结构.包括位置图(position map)、组管理单元(group management unit, GMU)、加密单元(Enc-pipe)、解密单元(Dec-pipe)、随机数生成器(random number generator, RNG)以及2个特殊缓冲区,数据缓存缓冲区(cache buffer, CBuffer)和组地址缓冲区(group address buffer, GAB).除了这些组件之外,还有1个读缓冲区(read buffer, RBuffer)和1个写缓冲区(write buffer, WBuffer)来保存内存读取和写入操作的数据.

位置图:提供每个逻辑数据块的当前物理地址.由于位置图的目的是映射每个数据块的当前位置,因此只要数据块的位置改变,该表就会更新.

CBuffer:暂时存放从内存读取的真实数据块,并且在对读取的数据块进行打乱重组时起关键作用.

GMU:保存每个数据块对应的组,若分组ORAM需要从片外内存访问某个数据块,则在GMU中找到该数据块对应的组,位置图将给出该组数据块物理地址,并将其发送到GAB.

GAB:保留当前操作的1组数据块的片外内存地址.因此,GAB的大小与组大小相同.

加/解密单元(encryption/decryption pipelines):为了保护数据机密性,每个数据块在被发送到片外内存之前都进行了加密.当从片外内存获取数据块时,需要将其解密.

RNG:在ORAM操作过程中,有6种类型的随机值r1~r6需要动态生成.

r1:位数为lb(N+D)(单位为b),用于初始化GMU,从而为每个数据块随机构建相应的组.

r2:位数为lbG(单位为b),用于在块置换期间为将要移动到WBuffer中的块选择新位置.其中G是组大小.每个ORAM操作总共需要G个不同的r2值.

r3:位数为lbC(单位为b),用于选择CBuffer中的位置以缓存从内存读取的真实数据块,其中C为CBuffer大小.每个ORAM操作都需要G个r3值.

r4:用于生成需要放入WBuffer的虚拟块.

r5:位数为lbG(单位为b),用于选择GAB中的位置,以放置数据块的物理地址PA.

r6:用于在重新加密相同明文数据块.

2.3 分组ORAM算法

在分组ORAM设计中,任何时候,真实数据块都位于片上CBuffer或片外内存中的某个位置.在对数据块进行访问时,如果块位于CBuffer,则不需要进一步的ORAM操作;

否则,将执行ORAM操作从片外内存中获取请求的块.

初始化时,CBuffer滞空,位置图存储每个数据块的当前位置.GMU为每个数据块构建其对应的组.图4(a)为1个简单的GMU存储示例,每个数据块都有其对应的组(在这个示例中,组大小G=3).并且每个数据块与组内其他数据块的关系可以用有向图表示,如图4(b)所示.以数据块A为例,数据块C和D被分配在该组内,在访问数据块A时,数据块A,C,D将形成一小簇数据块一同被ORAM控制器访问.为了隐藏访问模式,在数据块A被访问后,ORAM控制器将该组数据块在WBuffer内进行随机排列并写入片外内存,同时更新位置图以及GMU内数据块之间的关系.

为了从片外内存访问数据块,处理器将请求access(A,op,D)发送到分组ORAM控制器,其中数据块的逻辑地址是LA,op是读或写操作,如果是写操作,则D是要写入的数据.分组ORAM控制器遵循算法1中定义的数据访问协议oram_access,以隐藏对片外内存的真实访问.

图4 GMU存储示例

对于处理器的1次访问请求,ORAM控制器首先查找位置图以确定数据块的位置.如果块在片上,则在CBuffer上执行访问——如果是读操作,则将请求的数据发送给处理器进行读取,否则使用新数据更新缓冲区中的块.但是,如果块位于片外内存中,则执行ORAM操作,具体操作步骤由算法1给出.

算法1.oram_access:用于数据访问的分组ORAM协议.

输入:处理器请求(A,op,D)、位置图、组管理单元GMU、组大小G;

输出:执行对所请求的数据块的操作op.

① 在位置图中查找数据块A所在位置;

② if 数据块A在片上 then

③//片上访问

④ ifop==读操作 then

⑤ 在CBuffer内查找数据块A并将其返回给处理器;

⑥ else

⑦ 在CBuffer内查找数据块A并将其更新为D;

⑧ end if

⑨ goto end

⑩ else

3.1 安全性分析

由于数据块之间形成关系图保持不变,并且每次对1组数据块访问后,都将这组数据块与ORAM缓存中的块一同随机排列,所以每个数据块可以在整个关系图中以相同的概率出现在任意位置.因此,在整个内存空间的分配中,分组ORAM均匀随机地将数据块的逻辑地址映射到物理地址.此外,每个数据块在内存中都以密文的方式存储,并且数据块在被处理器访问后都需进行重新加密.因此攻击者在数据总线上窥探时不能得到任何显示信息.

为了访问某个数据块,分组ORAM首先找到其所在的组,并将该组数据块一并进行访问.这组数据块具有以下几个性质:1)内存空间中的任意数据块都以相同的概率可能出现在该组内;

2)组内数据块之间并无关联;

3)组内数据块以随机顺序被访问.因此,攻击者在窥探地址总线时无法知道请求块的真实位置.此外,组内的真实数据块在被访问后将以随机位置保存在CBuffer中,并且这些位置原有的数据块与虚拟数据块将以随机位置写回内存.这意味着,如果处理器再次请求相同的块,它将直接从CBuffer中读取,除非在访问该数据块时,该数据块已经被其他真实数据块替换并写回内存.

给定N个数据块的应用空间和D个数据块的虚拟空间,组大小为G.假设y是处理器请求内存的访问序列,其中包含m个请求块.对于y=(a1,a2,…,am),分组ORAM生成实际访问序列:

z=(G1,G2,…,Gm),

(1)

其中Gi表示数据块ai对应的组,每个组中包含G个需实际访问的数据块.

在数据块ai被访问后,它将暂时存放于CBuffer中,由于它在CBuffer中的位置是随机的,它被其他后续访问的数据块替换的顺序也是随机的,并且被替换后与组内其他数据块进行随机排列,形成新的组Gj,因此数据块ai下一次被访问时所在组的可能性的总数为

(2)

假设数据块ai下一次被访问时所在的组为Gj,Gj被选择的概率为

(3)

并且在组内,每个块都以概率1/G独立映射,利用贝叶斯原理,可以得到:对于访问序列y,分组ORAM根据y形成的2次实际访问序列z=z′的概率为

(4)

这个概率非常小,以至于实际访问序列z与z′在计算上无法区分,也就是说,对于某个访问序列y,攻击者几乎不可能观察到2次相同的实际访问序列.因此,攻击者无法知道真正的访问模式y.

3.2 开销分析

如前所述,现有ORAM方案面临的一个难题就是开销.在保证安全性的同时,这里对分组ORAM在内存带宽使用、访问延迟和内存空间消耗3个方面产生的开销进行分析.

内存带宽使用:从算法1可以看出,对于每次真实访问,分组ORAM从片外内存读取G个数据块,然后写入相同数量的数据块,导致每次真实访问总共使用2G块带宽.由于它是1个常数,并且作为参数可以设置,所以无论片外内存容量(或应用程序数据块总数)多大,内存带宽使用开销均为O(1).

访问延迟:对于每次真实访问,分组ORAM仅访问恒定的G个数据块,同时位置图以及GMU更新也都只针对常数量的数据块.因此,分组ORAM算法的延迟开销也为O(1).

由于内存带宽使用以及访问延迟带来的开销都为O(1),因此,分组ORAM的性能与应用程序或片外内存的大小无关.然而,片外内存的大小影响了位置图以及GMU的大小.

内存空间消耗:像大多数现有的ORAM方案一样,分组ORAM需要消耗额外的内存空间用于虚拟数据块.理想情况下,虚拟空间越大块位置越不可预测.但是,虚拟空间太大会导致片外和片上的大量存储消耗.本文尝试减少虚拟空间,同时为每次内存访问实现尽可能高的随机性,如下所示.

由于分组ORAM中可以使用的不同组的总数为S,如式(2)所示,因此,分组ORAM具有足够大的块空间供数据块打乱重组,并提供比其他现有ORAM方案更高的随机化能力,例如数据块只能打乱重组到N条路径上的Path ORAM.

给定组大小G,1个组包含1个虚拟数据块的概率为P1=D/(N+D),包含2个虚拟数据块的概率为P2=(D/(N+D))2,包含k个虚拟数据块的概率为Pk=(D/(N+D))k,其中k 如2.1节所述,分组ORAM使用CBuffer和WBuffer将数据块随机打乱重组写回内存,并且对于随机性,参与ORAM操作的虚拟块具有重要作用. 为了实现每个组中虚拟数据块数量的随机性,组中具有不同数量虚拟块的概率应尽可能接近.也就是说,概率比例r=Pi/Pi+1=(N+D)/D应尽可能小.该比例随着虚拟空间D的增加而减小,但存在1个肘点,如图5中的r曲线所示.肘点为最佳(最小)虚拟空间提供了良好的折中方案. 给定r曲线,要找到肘点,首先创建1条连接曲线2个端点的直线.肘点则位于从该直线到曲线形成最长直角距离的位置,如图5所示: 图5 r值与虚拟空间的关系 r曲线可以写成: (5) 其中y1表示比例,x表示虚拟空间大小,N作为常数表示应用程序数据空间大小. 2个端点可以近似为(0,N),(N,0),它们之间的连线可以表示为 y2=-x+N. (6) 由于r曲线的导数为y′=-N/x2,其中N>0,x2>0,所以y′<0.则r曲线单调递减.在r曲线上任意一点的切线,都与该点的曲率半径相垂直,而斜率相等的2条直线相互平行.因此,在r曲线y1上找一点,如果该点的切线的斜率与直线y2的斜率相等,那么该点的曲率半径垂直于直线y2,因此,该点就是所求的肘点. (7) 将式(7)代入式(5),得 (8) (9) 对于给定的应用程序,使用处理器模拟工具Simplescalar[19]对其在处理器上的执行进行模拟,从中获得处理器的内存访问序列(Las),分组ORAM使用Verilog HDL实现,并使用Xilinx vivado对Xilinx xc7vx330t FPGA平台进行仿真和综合.通过Xilinx仿真,可以得到分组ORAM输出的实际访问序列(PAs),然后使用NIST[20]测试套件检测内存总线上地址访问的随机性. 在实验中,将内存块大小B设置为128 b,内存块地址大小设置为18 b(N+D=218).加密算法选择国密算法SM2[21]进行加密和解密,SM2是基于基本椭圆曲线(ECC)密码的公钥密码算法标准,其安全强度比RSA高,且运算速度快于RSA.同时采用与文献[8]中使用的片外内存相同的模型,并使用线性反馈移位寄存器(LFSR)进行随机数生成. 下面将首先评估分组ORAM的性能开销,然后讨论生成的访问序列的随机性. 在实验中,研究了配置不同组大小和CBuffer大小时的性能开销.对于每种配置都执行Mibench基准测试程序组[22]的子集.对于每个基准测试,获得了没有分组ORAM的处理器系统以及集成了分组ORAM的处理器系统的执行时间.性能开销用执行速度降低μ来衡量,即使用分组ORAM时的执行时间与不使用分组ORAM时的执行时间之比,μ值越高说明执行速度的降低越明显. 如2.3节所述,如果在CBuffer中发现请求的数据块,分组ORAM不会执行片外内存访问.因此,除了数据打乱重组,CBuffer的大小C影响应用程序的总体执行时间.为了探究这种影响,测试了不同CBuffer大小的执行性能.从图6可以观察到,对于给定的组大小和CBuffer大小,执行时间之比μ都不同,具有良好局部性或较小工作数据集的基准测试程序(如CRC32)会产生较少的内存访问,因此它们的性能不会受到ORAM的太大影响.但对于一些基准测试程序,如Rijndael,执行速度会大幅降低.其次,执行各种基准测试程序时,对于不同CBuffer大小,μ值都有所变化,其中组大小G固定为16个数据块.可以观察到,每当CBuffer大小增加1倍,μ值会随之降低,当CBuffer大小较大时,μ值降低更明显.当CBuffer大小从256块增加到512块时,μ值降低了23.6%. 图6 当分组ORAM配置不同CBuffer大小时执行时间之比 决定性能开销的另一主要因素是组大小G.组大小与ORAM操作的延迟成正比.因此,在评估中纳入了分组ORAM组大小.图7示出给定CBuffer大小C=256的条件下,随着组大小的变化,执行时间之比μ的变化.从图7可以看出,当组大小增加时,μ值随之增加,即执行性能下降.这一趋势再次证实了预期的结果,即增加组大小会增加每个基准测试程序的完成时间.然而,由于处理器缓存中的高命中率,具有良好数据局部性或较小工作集的应用程序受到的影响相对较小. 图7 当分组ORAM配置不同组大小时执行时间之比 图8 当分组ORAM配置不同CBuffer大小时访问序列随机性变化 从图7还可以观察到,当组大小G从16增加到32时,执行时间之比μ会大幅增加,这意味着ORAM访问效率大幅下降,在4.3节将对最佳组大小G的选择进行分析. 分组ORAM生成的实际访问序列的随机性同时受组大小和CBuffer大小的影响.在执行每个基准测试程序期间,通过配置不同的组大小G和CBuffer大小C,获得了分组ORAM生成的内存访问序列.每个访问序列中的随机性都是通过NIST随机性测试套件评估的.对于每个内存访问序列,执行NIST测试套件中的所有测试,从而获得该访问序列的平均随机性通过率.更高的通过率意味着序列的随机性更高. 图8示出在给定组大小G为16个块时,CBuffer大小C如何影响生成的访问序列的随机性.同样,在给定CBuffer大小为256块时,图9显示了组大小G如何影响生成的访问序列的随机性.从图8可以看出,随机性与组大小和CBuffer大小成正比.这是因为增加组大小会在每次ORAM操作中打乱重组更多数据块,而增加CBuffer大小会提供更多的片上数据打乱重组空间. 从图9还可以发现,组大小G从16增加到32时,随机性通过率的变化并不明显.这意味着当组大小达到16时,安全性已经到达瓶颈,再增加组大小只会造成性能大幅下降,如4.1节所述. 图9 当分组ORAM配置不同组大小时访问序列随机性变化 下面,将分组ORAM与目前最先进的设计方案Tiny ORAM[8]进行比较.表2示出两者在FPGA资源消耗方面的开销——查找表(LUT)、触发器(FF)和块RAM(BRAM)数量.表3示出两者在每次内存访问时操作效率方面的比较. 表2 2种方案在FPGA资源消耗方面的比较 表3 2种方案在1次内存访问时操作效率方面的比较 从表2可以看出,分组ORAM消耗较少的为FF,LUT和BRAM相对较多.而从表3可以看出,对于每次内存访问,分组ORAM需要0.29~0.34 μs.与Tiny ORAM相比,延迟降低了75.7%~79.3%. 本文提出了一种ORAM方案——分组ORAM,它将真实内存访问隐藏在对一小簇内存地址的虚拟访问中,从而达到隐藏内存访问模式的目的.该方案使用缓冲区来解耦读取和写入之间的块,从而使每个组不相关.此外,该方案引入了参数化设计,可以调整参数以满足不同平台对性能、安全性的需求.通过执行Mibench基准测试程序来评估该方案的性能,并使用NIST测试生成的片外内存访问序列的随机性评估该方案的安全性.实验结果表明,相较之前的工作,分组ORAM方案能显著减少性能开销.同时,针对组大小为8~32个数据块和CBuffer大小为64~512个数据块的不同配置,其生成的内存访问序列随机性测试通过率达到94.6%~98.5%.与现有方案相比,分组ORAM在性能、安全性和内存消耗方面的表现都有所提升.

4.1 性能评估

4.2 安全性评估

4.3 比 较

- 范文大全

- 说说大全

- 学习资料

- 语录

- 生肖

- 解梦

- 十二星座

-

主题党日活动交流发言8篇

主题党日活动交流发言8篇主题党日活动交流发言篇13月13日,东城区党史学习教育动员大会召开。市委

【活动总结】 日期:2022-12-23

-

2022年4月主题党日活动记录范文15篇

2022年4月主题党日活动记录范文15篇2022年4月主题党日活动记录范文篇1一个崇尚阅读的民族,必然精神饱满、意气风发、活力四射。习近平总书记强调:“学习

【活动总结】 日期:2022-08-01

-

家乡赋|最美的家乡赋

家乡赋 孙传志 今安康市,白河双丰镇,吾之家乡也。三环沃土,山水环抱。其北依山,山系五岭,山

【调研报告】 日期:2020-04-01

-

【人教版1-6年级数学上册知识点精编】1-6年级数学人教版教材

人教版二年级数学上册知识点汇总第一单元长度单位一、米和厘米1、测量物体的长度时,要用统一的标准去测量

【调研报告】 日期:2020-11-08

-

党支部1-12月全年主题党日活动计划表

2022年党支部主题党日活动计划表序号活动时间活动方式活动内容12022年1月专题学习研讨集中观看2022年新年贺词,积极开展学习研讨交流。组织生活会组织党员认真对照党章...

【活动总结】 日期:2022-10-14

-

2022年2月份主题党日活动记录5篇

2022年2月份主题党日活动记录5篇2022年2月份主题党日活动记录篇1尊敬的党组织:在今年的开学初,本人积极参加教研室组织的教研活动,在学校教研员的指

【活动总结】 日期:2022-08-12

-

少先队的光荣历史故事 队前教育-光辉历程

2017-2018学年队前教育1光辉历程一、劳动童子团1924——1927二、三十年代年的中国是一个

【法律文书】 日期:2020-06-23

-

2023年平安校园建设方案13篇

平安校园建设方案“平安校园”创建工作,我们幼儿园全体教职员工一直把它当作头等大事来抓。领导高度重视,以“平安校园”创建活动为抓手,建立和规范校园安全工作机制

【规章制度】 日期:2023-11-02

-

医院最佳主题党日活动11篇

医院最佳主题党日活动11篇医院最佳主题党日活动篇1 医院最佳主题党日活动篇2为隆重纪念中国共产党成立100周年,进一步巩固党的群众路线教育实践活动成果,切实

【活动总结】 日期:2022-10-29

-

主题党日活动记录202210篇

主题党日活动记录202210篇主题党日活动记录2022篇12021年是中国共产党成立100周年,为广泛开展爱国主义宣传教育,铭记党的历史,讴歌党的光辉历程,

【活动总结】 日期:2022-08-02

-

正式的晚宴邀请函 公司晚宴邀请函

尊敬的先生 女士: 我公司谨定于xxxx年xx月xx日xx:xx在xxxx店隆重举行xx市xx届xxxx晚宴(宴会地址:xx区xx路xxxx) 敬请届时光临!xxxxxx集团股份有限公司xxxx有限公司敬邀xxxx年xx月xx日

【简历资料】 日期:2019-08-03

-

一年级新学期目标简短_一年级学生新学期打算

新学期到了,我是一年级下册的小学生了。 上课的时候,我要认真学习,不做小动作,认真听讲。我要认真学习,天天向上,努力学习,耳朵要听老师讲课,眼睛要瞪得大大的看老...

【简历资料】 日期:2019-10-26

-

[信访复查复核制度作用探讨]信访复查复核有用吗

作为我国特有的一项制度,信访制度的出现并长期存在不是偶然的,虽然一些法学专家认为信访制度具有“人治”

【职场指南】 日期:2020-02-16

-

[党员干部2019年主题教育个人问题检视清单及整改措施2篇] 党员干部

2019年主题教育问题检视清单及整改措施根据主题教育领导小组办公室《关于认真做好主题教育检视问题整改

【求职简历】 日期:2019-11-08

-

网络维护工作内容_(精华)国家开放大学电大专科《网络系统管理与维护》形考任务1答案

国家开放大学电大专科《网络系统管理与维护》形考任务1答案形考任务1理解上网行为管理软件的功能【实训目

【职场指南】 日期:2020-07-17

-

党委会与局长办公会的区别_局长办公会制度

为进一步加强xxx局工作的规范化、制度化建设,提高行政效能,规范议事程序,特制定本制度。一、会议形式1、局长办公会议由局长、副局长参加。由局长召集和主持。根据工作需要...

【求职简历】 日期:2019-07-30

-

《铁拳砸碎“黑警伞”》警示教育片观后感

影片深刻剖析了广西北海市公安局海西派出所原所长张枭杰蜕变堕落的轨迹。观看警示教育片后,做为一名党员教

【简历资料】 日期:2020-08-17

-

如何凝心聚力谋发展【坚定信心谋发展凝心聚力促跨越】

当前,清河正处于在苏北实现赶超跨越基础上全面腾飞的战略机遇期,处于在全市率先实现全面小康基础上率先实

【简历资料】 日期:2020-03-17

-

学生会组织部部长竞选稿5篇

学生会组织部部长竞选稿以“三制”为统领推进农村党的建设中共**市委组织部近年来,**市认真落实中央、省和徐州市委的部署,积极适应发展要求,从加强领导体制、运

【求职简历】 日期:2023-11-06

-

系领导班子行为准则_必须以什么为行为准则

为了更好地完成本系的各项工作,充分发挥系领导班子的模范带头作用,特制定本行为准则如下:一、要勤政为民,真抓实干,坚持科学态度和求实的精神,兢兢业业地作好本职工作。...

【求职简历】 日期:2019-08-30

-

【乡镇XX年安全生产工作总结】 两会期间乡镇安全生产工作总结

乡镇xx年安全生产工作总结 xx年,北宿镇党委、政府以党的十六大和“三个代表”重要思想为指导,以实施《安全生产法》,为主题,认真贯彻落实上级安全生产工作一系列指示精...

【导游词】 日期:2019-09-08

-

在县委巡察组向县总工会党组反馈巡察情况会上的表态发言(全文完整)

在县委巡察组向县总工会党组反馈巡察情况会上的表态发言各位领导、同志们:按照县委统一部署,县委委第*巡察组于2021年11月11日进驻我单位开展巡察工作。今天,巡察组的各位领...

【其他范文】 日期:2022-10-30

-

部长竞选演讲稿【竞选秘书处副处长的激情演讲稿】

导读:竞选演讲稿范文,竞选秘书处副处长的激情演讲稿应该怎么写,有什么格式要求,科教范文网提供的这篇文章是一个很好的范例:尊敬的各位领导、各位同事: 首先,我要特...

【毕业论文】 日期:2019-10-15

-

HX乡镇干部谈党的会议精神学习体会

HX乡镇干部谈党的会议精神学习体会

【其他范文】 日期:2022-09-17

-

2022年度小学四年级数学上学期培优辅差工作总结范本(2022年)

当前位置:>>2021-10-03本学期本人根据四年级学生的情况,对个别优生进行培养,发挥优生的所长,使优生更优,并对差生进行教育,提高差生的学习积极性,使差生变优,根据学校的...

【其他范文】 日期:2022-09-01

-

2023年自来水公司优秀支部和先进个人事迹报告_先进个人【完整版】

2020自来水公司个人先进事迹材料报告1梅花,以其高洁的品质,为历代文人墨客所称颂。而自来水公司党支部领导班子在创先争优活动中就像宝剑的锋刃一样,经过千锤百炼,以其廉洁...

【其他范文】 日期:2023-09-16

-

医学期刊专栏吸引优质稿件建设及成效——以《公共卫生与预防医学》期刊为例

万美,赵珣,刘杨铭,吴海平,易秋莎(湖北省疾病预防控制中心《公共卫生与预防医学》期刊编辑部,湖北武汉

【其他范文】 日期:2023-04-08

-

积极心理学视阈中的资助育人

尹杰(南京财经大学公共管理学院江苏南京210023)研究表明:一个人的幸福指数与他的财富和社会地位并

【其他范文】 日期:2023-06-30

-

2022年县政府办党组书记抓基层党建述职报告(全文完整)

今年来,在县委、县政府的正确领导下,我坚持围绕中心、建设队伍、服务群众推动党建工作,切实履行党组书记抓基层党建工作第一责任人的职责,团结办公室党组班子,在办公室全...

【其他范文】 日期:2022-10-08

-

(2篇)在传达2022年全国两会精神会议上的讲话

下面是小编为大家整理的(2篇)在传达2022年全国两会精神会议上的讲话[标签

【其他范文】 日期:2022-10-18

-

军转座谈会交流发言4篇

军转座谈会交流发言4篇军转座谈会交流发言篇1大家好,我叫贺丽,2015届选调生,来自康定市委组织部,现在省委编办跟班学习。今天,非常荣幸向大家汇报我的学习收

【发言稿】 日期:2022-10-27

-

12岁生日小寿星发言4篇

12岁生日小寿星发言4篇12岁生日小寿星发言篇1各位来宾、各位朋友:大家好!今天,我们欢聚在这里,共同庆祝**十二周岁生日。首先,我代表**的父母以

【发言稿】 日期:2022-07-31

-

廉政大会总结发言稿7篇

廉政大会总结发言稿7篇廉政大会总结发言稿篇1各位领导,同志们:根据会议安排,我就党风廉政建设工作做表态发言,不妥之处,请批评指正。一、提高认识,切实

【发言稿】 日期:2022-10-30

-

被约谈的表态发言8篇

被约谈的表态发言8篇被约谈的表态发言篇1各位领导、各位党员大家好:这天我能站在鲜红的党旗下,

【发言稿】 日期:2022-12-24

-

破冰提能大讨论个人发言4篇

破冰提能大讨论个人发言4篇破冰提能大讨论个人发言篇1党史学习教育开展以来,我坚持读原著、学原文、悟原理。今天,根据会议安排,现在我就“学史明理”主题谈几点个

【发言稿】 日期:2022-10-09

-

我最敬佩的人开头_我敬佩的一个人作文20篇2020年

我敬佩的一个人作文20篇 我敬佩的一个人作文一): 我身边有很多值得我们敬佩的人,但我最敬佩的一

【发言稿】 日期:2020-11-10

-

党员教育培训总结交流发言12篇

党员教育培训总结交流发言12篇党员教育培训总结交流发言篇1根据市委组织部《关于开展我市〈20XX

【发言稿】 日期:2022-12-19

-

纪委书记工作表态发言4篇

纪委书记工作表态发言4篇纪委书记工作表态发言篇1在镇党委政府正确领导下,在全村干部和群众的共同努力下,紧紧围绕建设社会主义新农村工作为重点,尽职尽责,与时俱

【发言稿】 日期:2022-09-30

-

[钻井队队长(副队长、指导员)岗位HSE应知应会试题(1863)]

钻井队队长(副队长、指导员)岗位HSE应知应会试题(判断题:771;单选题:626;多选题:466)

【贺词】 日期:2020-09-23

-

话剧《家》剧本 话剧剧本:爱的空间

找文章到更多原创-(http: www damishu cn)人物介绍:刘伟,男,32岁,某购物广

【演讲稿】 日期:2020-01-21

-

学习周永开先进事迹心得体会3篇

学习周永开先进事迹心得体会【一】通过学习周永开老先生先进事迹后,结合自己工作思考,感慨万千。同样作为

【格言】 日期:2021-04-10

-

XX老干局推进党建与业务深度融合发展工作情况调研报告:党建调研报告

XX老干局推进党建与业务深度融合 发展工作情况的调研报告 党建工作与业务工作融合发展始终是一个充满生

【成语大全】 日期:2020-08-28

-

中国共产党第三代中央领导集体的卓越贡献

中国共产党第三代中央领导集体的卓越贡献 --------------继往开来铸就辉煌 【摘要】改

【成语大全】 日期:2020-03-20

-

2023年中国行政区划调整方案(设想优秀3篇

中国行政区划调整方案(设想优秀民政部第二次行政区划研讨会会议内容一、缩省的意义与原则1.意义1)利于减少中间层次中国行政区划层级之多为世界之最,既使管理成本

【周公解梦】 日期:2024-02-20

-

信息技术2.0能力点 [全国中小学教师信息技术应用能力提升工程试题题库及参考答案「精编」]

全国中小学教师信息技术应用能力提升工程试题题库及答案(复习资料)一、判断题题库(A为正确,B为错误)

【格言】 日期:2020-11-17

-

党建工作运行机制内容有哪些_构建基层党建工作运行机制探讨

党的基层组织是党在社会基层组织中的战斗堡垒,是党的全部工作和战斗力的基础。加强和改进县级以下各类党的

【经典阅读】 日期:2020-01-22

-

集合推理_七,推理与集合

七推理与集合1 期中考试数学成绩出来了,三个好朋友分别考了88分,92分,95分。他们分别考了多少分

【名人名言】 日期:2020-12-18

-

电大现代教育原理_最新国家开放大学电大《现代教育原理》形考任务2试题及答案

最新国家开放大学电大《现代教育原理》形考任务2试题及答案形考任务二一、多项选择题(共17道试题,共3

【成语大全】 日期:2020-07-20

-

基层党务工作基本内容_党建基本工作有哪些

党建基本工作有哪些(一) 基层党建工作包括哪些内容 选择了大学生村官这条路,你就与农村基层党

【名人名言】 日期:2020-08-06

-

【2020-2021学年高一英语外研版(2019)选择性必修第一册Unit3Faster,higher,strongerSectionⅠ导学讲义】

Unit3 Faster,higher,stronger背景导学MichaelJordan—Head

【歇后语】 日期:2021-04-19

-

关于三农工作重要论述心得体会3篇

关于三农工作重要论述心得体会3篇关于三农工作重要论述心得体会篇1习近平总书记指出:“建设现代化国家离不开农业农村现代化,要继续巩固脱贫攻坚成果,扎实推进乡村

【学习心得体会】 日期:2022-10-29

-

【福生庄隧道坍塌处理方案】 福生庄隧道在哪里

(呼和浩特铁路局大包电气化改造工程指挥部,内蒙古呼和浩特010050)摘要:文章介绍了福生庄隧道

【学习心得体会】 日期:2020-03-05

-

五个一百工程阅读心得体会13篇

五个一百工程阅读心得体会13篇五个一百工程阅读心得体会篇1凡益之道,与时偕行。在全国网络安全和信

【学习心得体会】 日期:2022-12-07

-

城管系统警示教育心得体会9篇

城管系统警示教育心得体会9篇城管系统警示教育心得体会篇1各党支部要召开多种形式的庆七一座谈会,组织广大党员进行座谈,回顾党的光辉历程,畅谈党的丰功伟绩,

【学习心得体会】 日期:2022-10-09

-

发展对象培训主要内容10篇

发展对象培训主要内容10篇发展对象培训主要内容篇1怀着无比激动的心情,我有幸参加了__新区区委党校20__年第四期(区级机关)党员发展对象培训班。这次的学习

【培训心得体会】 日期:2022-09-24

-

凝聚三种力量发展全过程人民民主心得体会12篇

凝聚三种力量发展全过程人民民主心得体会12篇凝聚三种力量发展全过程人民民主心得体会篇1新民主主义革命是指在帝国主义和无产阶级革命时代,殖民地半殖民地国家中的

【学习心得体会】 日期:2022-08-31

-

2022年全国检察长会议心得7篇

2022年全国检察长会议心得7篇2022年全国检察长会议心得篇1眼睛是心灵上的窗户,我们通过眼睛才能看到世间万物,才能看到眼前这美好的一切。拥有一双明亮的眼

【学习心得体会】 日期:2022-10-31

-

在街道深化作风建设推动高质量发展走在前列动员会上讲话

在2023年街道深化作风建设推动高质量发展走在前列动员会上的讲话同志们:今天我们召开“街道深化作风建设推动高质量发展走在前列动员会”,这次会议是街道三季度召开的第一场...

【军训心得体会】 日期:2024-03-17

-

全面从严治党的心得体会800字7篇

全面从严治党的心得体会800字7篇全面从严治党的心得体会800字篇1中国特色社会主义是我们党领导

【学习心得体会】 日期:2022-12-14

-

矫正心得体会6篇

矫正心得体会6篇矫正心得体会篇1今天,是自己出监后第一次参加阳光中途之家组织的社区矫正方面的教育

【学习心得体会】 日期:2022-12-24

-

2024年主题教育民主生活会批评与自我批评意见(38条)(范文推荐)

2024年主题教育民主生活会批评与自我批评意见(38条)(范文推荐)

2023年主题教育民主生活会六个方面个人检视、相互批评意见:1 理论学习系统性不强。学习习近平新时代中国特色社会主义思想不深不透,泛泛而学的时候多,深学细照的时候少,特...

【邓小平理论】 日期:2024-03-19

-

2024年交流发言:强化思想理论武装,增强奋进力量(完整)

2024年交流发言:强化思想理论武装,增强奋进力量(完整)

习近平总书记指出:“一个民族要走在时代前列,就一刻不能没有理论思维,一刻不能没有思想指引。”党的十八大以来,伴随着新时代中国特色社会主义思想在实践中形成发展的历程...

【三个代表】 日期:2024-03-19

-

2024年度镇年度县乡人大代表述职评议活动总结

2024年度镇年度县乡人大代表述职评议活动总结

xx镇20xx年县乡人大代表述职评议活动总结为响应县级人大常委会关于开展县乡两级人大代表述职评议活动,进一步激发代表履职活力,加强代表与人民群众的联系,提高依法履职水平...

【马克思主义】 日期:2024-03-19

-

“千万工程”经验学习体会(研讨材料)

“千万工程”经验学习体会(研讨材料)

“千万工程”是总书记在浙江工作时亲自谋划、亲自部署、亲自推动的一项重大决策,也是习近平新时代中国特色社会主义思想在之江大地的生动实践。20年来,“千万工程”先后经历...

【三个代表】 日期:2024-03-19

-

2024年在市政协机关工作总结会议上讲话

2024年在市政协机关工作总结会议上讲话

同志们:刚才,XX同志对市政协机关20XX年工作进行了很好的总结,很精炼,很到位,可以感受到去年机关工作确实可圈可点。XX同志宣读了表彰决定,机关优秀人员代表、先进集体代...

【邓小平理论】 日期:2024-03-18

-

在全区防汛防涝动员暨河长制工作推进会上讲话提纲【完整版】

在全区防汛防涝动员暨河长制工作推进会上讲话提纲【完整版】

区长,各位领导,同志们:汛期已经来临,我区城区防涝工作面临强大考验,形势不容乐观。年初,区城区防涝排渍指挥部已经召开专题调度会,修订完善应急预案,建立网格化管理机...

【马克思主义】 日期:2024-03-18

-

2024年镇作风整治工作实施方案(完整文档)

2024年镇作风整治工作实施方案(完整文档)

XX镇作风整治工作实施方案为深入贯彻落实党的二十大精神及省市区委深化作风建设的最新要求,突出重点推进干部效能提升,坚持不懈推动作风整治工作纵深发展,根据《关于印发《2...

【毛泽东思想】 日期:2024-03-18

-

2024市优化法治化营商环境规范涉企行政执法实施方案【优秀范文】

2024市优化法治化营商环境规范涉企行政执法实施方案【优秀范文】

xx市优化法治化营商环境规范涉企行政执法实施方案为持续优化法治化营商环境,激发市场主体活力和社会创造力,规范行政执法行为,创新行政执法方式,提升行政执法质效,着力解...

【毛泽东思想】 日期:2024-03-18

-

2024年度关于开展新一轮思想状况摸底排查工作通知(完整)

2024年度关于开展新一轮思想状况摸底排查工作通知(完整)

关于开展新一轮思想状况摸底排查工作的通知为深入贯彻落实关于各地开展干部职工思想状况大摸底大排查情况上的批示要求和改革教育第二次调度会议精神,有针对性做好队伍教育管...

【三个代表】 日期:2024-03-18

-

2024年公路养护中心主任典型事迹材料(完整文档)

2024年公路养护中心主任典型事迹材料(完整文档)

“中心的工作就是心中的事业”——公路养护中心主任典型事迹材料**,男,1976年6月出生,1993年参加工作,2000年4月调入**区交通运输局工作,大学本科学历,中共党员,现任**...

【马克思主义】 日期:2024-03-17